英特尔、AMD下一代处理器架构解析

没错,英特尔、AMD又到了产品升级换代的时候了。英特尔的Tick-Tock到了Tock这一步,新产品Haswell箭在弦上;AMD虽然暂时落后一局,但新的压路机也是曙光在前,蓄势待发。那么,究竟Haswell和压路机都有哪些改进?英特尔和AMD的竞争又会开发出哪些新技术呢?本文将带你提前了解英特尔和AMD的下一代处理器架构。

Haswell——小改进,大步伐

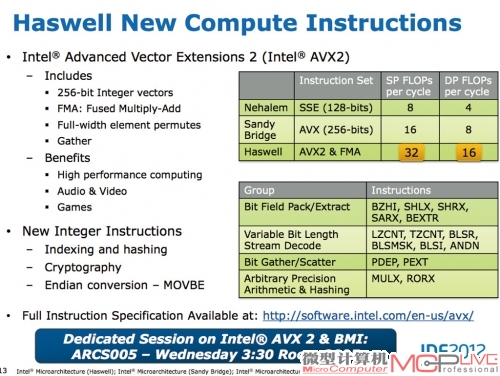

从英特尔发布了基于Core Microarchitecture(酷睿微架构)的Core 2 Duo系列到现在,英特尔对处理器内部核心架构的改进并不算大。从Core 2 Duo,到Nehalem Core i7,然后到Westmere、Sandy Bridge直到今天的Ivy Bridge,CPU微架构都可以算作是酷睿微架构的继承和发展,更多的变化则是工艺、总线、缓存等外围部件。在Ivy Bridge后,英特尔执行的是“Tick-Tock”中的“Tock”战略,这意味着Ivy Bridge的继承人“Haswell”所面对的目标是“使用成熟工艺,升级CPU架构”。除了处理器外,Haswell处理器将搭配代号为Lynx Point的主板芯片组,组成Shark Bay计算平台。

Haswell属于Tock部分,工艺不变(实际上也升级了),架构进步。

从目前掌握的消息来看,Haswell相比Sandy Bridge来说,在CPU架构方面改进大的当属加入了新的、有利于多线程执行的TSX扩展,以及大幅度提升整数计算性能的AVX 2.0技术。除此之外,Haswell在工艺方面也有所改进,当然CPU内部一些组件也会做出微小调整,但对整个CPU架构的影响不大。另外,在集成图形处理器方面,Haswell的图形性能会有比较明显的增长,EU单元数量会增加,功能上会进一步支持Direct X11. 1。在结构和扩展性能方面,Haswell在接口、封装模式上会做出一系列改动,CPU内部集成的电压控制单元会有改进,芯片组方面会采用更新的8系列芯片组。对玩家的一个好消息是,Haswell有望实现一定幅度的自由超外频。

TSX和AVX 2.0进驻——Haswell的CPU架构改进

Haswell的CPU架构改进主要集中在对CPU应用的改进上,本身硬件基础如传统的四发射设计、分支预测、内存控制器、缓存设计等部分的改进都比较小。因此本文的介绍重点也会集中在Haswell新增的TSX和AVX 2.0功能上。

可用、安全的细粒度线程锁定——TSX扩展

说起TSX的功能,先要从CPU超线程技术讲起。CPU超线程技术的主要目的是在CPU的一个处理核心中,同时运行多个线程。这项技术的思想来源甚至可以追溯到上个世纪90年代的“指令并行化”思想。

从技术发展的角度来看,类似“指令并行化”在发展过程中出现了诸如粗粒度多线程(Coarse-Grained Multi-Threading)、细粒度多线程(Fine-Grained Multi-Threading)和同步多线程(Simultaneous Multi-Threading)等多种方式,这些方式各有特色,也各有优劣。

所谓粗粒度多线程,是指在单一线程操作过程中,如果遇到某线程长时间延迟,那么立刻将此线程锁定并切换到另一线程,执行完后再切换回来。举个例子来说,粗粒度多线程类似于如下情况:在公用服务器上有一个文件夹,里面有100个文件。当A用户修改文件夹中任何一个文件时,整个文件夹会被锁定并进入只读状态,当B用户要访问文件夹时,他只能读取、复制文件夹内的文件,但无法修改。

粗粒度多线程是相当容易实现的一种多线程方案。这种方案的优势在于控制起来很简单,不容易出现冲突,但相对来说,粗粒度多线程“竞争损耗”比较大。所谓“竞争损耗”是指多个并行线程由于锁定等问题,终并行化不理想,操作中串行化大于并行化,终带来的性能增益很微小。

为了解决这个问题,细粒度多线程开始出现。它是指在每个时钟周期内,多个线程并行切换操作。依旧使用上文的例子来解释细粒度多线程:公用服务器上的文件夹中有100个文件,A修改文件夹的0号文件时,其余的99个文件并不会被锁定,B如果想修改3号文件,依旧可以自行修改。这样的锁定“粒度”相比之前的案例要小很多,可以锁定发生在更为细微的单个文件上,而不是整个文件夹。

细粒度多线程相比粗粒度多线程,对线程的控制更为细致,理论上并行度更好,但实际上细粒度多线程对程序的锁定更为细致,因此编程更为复杂,更容易出现错误和冲突。此外,细粒度多线程由于经常需要来回切换线程,每一次切换会浪费一定的时间,因此在单任务性能上细粒度多线程可能不如粗粒度多线程。总的来看,无论是细粒度还是粗粒度,都各自有优缺点,不能一概而论。

下面回归主题,目前处理器使用的多线程技术由于编程难度等问题,多使用粗粒度多线程,程序员只要在多个线程有可能冲突时直接锁定某线程即可。但这种粗粒度多线程在当前的应用环境下对性能提升的帮助有限,特别是对CPU多线程性能提升不大。实际上早在IDF 2006上,英特尔提出未来的处理器将使用事务型内存(Transactional Memory)和一些扩展技术来加强多线程的性能。所谓事务型内存,英特尔在这里应该并非是指物理内存或者与之相配的硬件设计要做出重大变化,而是指在程序编制过程中内存控制和使用的方法要改进为事务型内存的所代表的方法,也就是软事务型内存,其主要内容是原子对象和冲突判决器。简单来说,事务型内存的作用是针对不同事务(可以简单理解为线程)处理进行判断和沟通,并且在事务出错时能够回到之前的状态,从而在多任务并行处理时尽量避免发生错误。

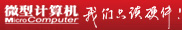

在提出事物型内存后,英特尔又发布了一篇名为“Transactional Synchronization in Haswell”的文章,介绍了下一代Haswell上即将使用的TSX扩展。TSX的作用很明确,就是搭配事务型内存使用,为未来的CPU提供更强大的多线程能力。英特尔认为,在使用了事务型内存、并采用了TSX扩展后,TSX扩展能够自动判断、评估软硬件的情况。在使用细粒度线程锁时,TSX扩展能够帮助程序员实现更为简单、准确的无错细粒度线程锁。根据英特尔数据,在使用了事务型内存和TSX扩展后,部分锁操作的性能可提升1~3倍。在软件仿真中,比如事务型内存锁操作只需要4.6秒,而传统内存需要高达10.6秒,性能提升显而易见。

当然,采用TSX扩展后,性能提升并非马上体现。TSX扩展的应用场合和内容都比较复杂,需要软件、硬件的全面配合,并且目前的软件基本上不会在TSX扩展中带来明显的性能增益。只有那些符合英特尔要求的软件,才能在多线程应用中有相当明显的、相对于传统编程方法的性能提升,这属于软件普及和应用的道路问题,还相当漫长。

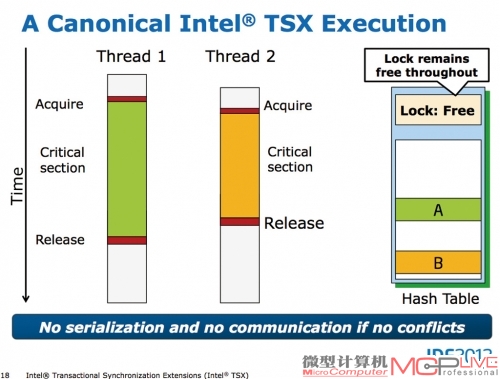

整数和浮点性能继续提升——AVX 2.0

AVX是Advanced Vector Extensions高级矢量扩展的简写,AVX在之前的Sandy Bridge和Ivy Bridge上就已经开始使用。目前的AVX指令集主要是用于增强浮点计算性能,它使用了256bit SIMD浮点指令集,支持三位数和四位数操作,也支持VEX编码方式。新的256bit浮点计算以及各种特色功能等相比前代的128bit有了巨大提升,在理想的情况下,256bit一次可以读更多的指令,浮点性能高提升可以达到128bit的2倍。另外,目前的新软件也开始使用AVX指令集来提升浮点计算能力,增强计算效能。

Haswell的芯片面积并不大,图为早前流传出的Haswell对比Ivy Bridge、Sandy Bridge等处理器的核心晶片。

在新的AVX 2.0中,英特尔也将整数计算部分升级到256bit SIMD阵列,CPU的整数计算性能得到大幅度提高,此外还添加了一些新的指令用于继续加强浮点性能。之前Sandy Bridge和Ivy Bridge不支持的FMA浮点乘积累(Floating Point Multiply Accumulate),在Haswell中终于给予支持。不过英特尔支持的FMA指令依旧是FMA3,AMD则更进一步支持FMA4(FMA4相比FMA3,除了在数据格式要求上更为灵活一些外,和FMA3相比只是一种计算的两个方面而已,并非换代性技术)。不过英特尔则认为FMA3已经能够提供更高的峰值速度,在高性能计算、图形处理等计算中有不错效果。

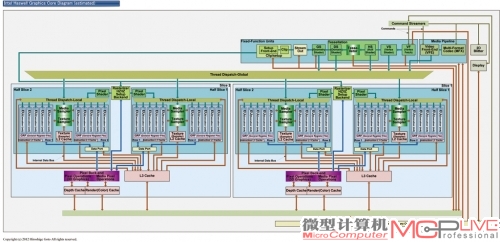

业内人士根据英特尔公布的Hawell的GPU部分架构图画出的详细架构内容,相比Ivy Bridge的GPU部分基本没太大变化。

AVX 2.0除了256bit整数计算以及FMA指令的加入外,还额外增加了不少用于加强计算、降低编程难度和提高精度的指令集,比如任意到任意排列(Any-to-Any permutes)、矢量位移(Vector-Vector Shifts)、Gather/Scatter指令以及3操作数通用位处理指令(3-operand generalpurpose Bit manipulation instructions)等。这些指令的加入,使得CPU可以在数据压缩、大规模计算、图形处理中速度更快,对程序员来说,编程过程也可能由于新指令集的使用而更为简单轻松。根据英特尔的数据,AVX 2.0搭配Haswell(L1缓存带宽从前代的48Byte/cycle增加到Haswell的96Byte/cycle,L2从32Byte/cycle增加到64Byte/cycle)后,CPU的每个核心、每时钟周期的单精度和双精度浮点理论高性能翻了一番,每个核心、每时钟周期的计算能力分别达到了32FLOPs和16FLOPs。再考虑CPU的高频率和多核心,在浮点能力方面Haswell将继续大幅度前进。